# SPECIFICATIONS FOR LCD MODULE

| CUSTOMER          |                     |

|-------------------|---------------------|

| CUSTOMER PART NO. |                     |

| AMPIRE PART NO.   | AM-240320LGTNQW-00H |

| APPROVED BY       |                     |

| DATE              |                     |

☑ Approved For Specifications□Approved For Specifications & Sample

AMPIRE CO., LTD.

4F., No.116, Sec. 1, Xintai 5th Rd., Xizhi Dist., New Taipei City 221, Taiwan (R.O.C.)

22181 新北市 汐止區 新台五路一段 116 號 4 樓(東方科學園區 A 棟) TEL:886-2-26967269, FAX:886-2-26967196 or 26967270

# RECORD OF REVISION

| Revision Date | Page     | Contents                                                                                                       | Editor  |

|---------------|----------|----------------------------------------------------------------------------------------------------------------|---------|

| 2011/08/19    | -        | New Release                                                                                                    | Rober   |

| 2011/09/29    | 11<br>12 | Redefine PIN 7 SDI Function<br>"Serial bus interface data input/output pin."<br>Redefine PIN 46 GND<br>SDO→GND | Rober   |

| 2012/2/1      | 11       | Correct Interface mode                                                                                         | Rober   |

| 2014/5/22     | 6        | Add LED life time                                                                                              | Patrick |

| 2015/07/06    | 7        | Corrected the LCM brightness.                                                                                  | Emil    |

|               |          |                                                                                                                |         |

### 1 Features

LCD 2.4 inch Amorphous-TFT-LCD (Thin Film Transistor Liquid Crystal Display) for mobile-phone or handy electrical equipments.

(1) Construction: 2.4" a-Si color TFT-LCD, White LED Backlight and FPCB.

- (2) Main LCD : 2.1 Amorphous-TFT 2.4 inch display, transmissive, Normally white type, 12 o'clock.

- 2.2 240(RGB)X320 dots Matrix, 1/320 Duty.

- 2.3 Narrow-contact ledge technique.

- 2.4 Main LCD Driver IC: HX8347-D

- 2.5 262K: Red-6bit, Green-6bit, Blue-6bit (18-bit interface)

- (3) Low cross talk by frame rate modulation

- (4) Direct data display with display RAM

- (5) Partial display function: You can save power by limiting the display space.

- (6) Interface: MPU and RGB Interface. (Select by H/W Jumper). Default : SPI

|                  | JP0(IM | 0)    | JP1(IM | JP1(IM1) |       | JP2(IM2) |       | 3)    | Remark  |

|------------------|--------|-------|--------|----------|-------|----------|-------|-------|---------|

| Interface mode   | R1(H)  | R2(L) | R3(H)  | R4(L)    | R5(H) | R6(L)    | R7(H) | R8(L) |         |

| 80-16BIT Type I  | NC     | 0R    | NC     | 0R       | NC    | 0R       | NC    | 0R    |         |

| 80-8BIT Type I   | 0R     | NC    | NC     | 0R       | NC    | 0R       | NC    | 0R    |         |

| 80-16BIT Type II | NC     | 0R    | 0R     | NC       | NC    | 0R       | NC    | 0R    |         |

| 80-8BIT Type II  | 0R     | NC    | 0R     | NC       | NC    | 0R       | NC    | 0R    |         |

| 3-wire SPI       | NC     | 0R    | NC     | 0R       | 0R    | NC       | NC    | 0R    | Default |

| 4-wire SPI       | -      | -     | 0R     | NC       | 0R    | NC       | NC    | 0R    |         |

| 80-18BIT Type I  | NC     | 0R    | NC     | 0R       | NC    | 0R       | 0R    | NC    |         |

| 80-9BIT Type I   | 0R     | NC    | NC     | 0R       | NC    | 0R       | 0R    | NC    |         |

| 80-18BIT Type II | NC     | 0R    | 0R     | NC       | NC    | 0R       | 0R    | NC    |         |

| 80-9BIT Type II  | 0R     | NC    | 0R     | NC       | NC    | 0R       | 0R    | NC    |         |

(7) Abundant command functions:

Area scroll function

Display direction switching function

Power saving function

Electric volume control function: you are able to program the temperature compensation function.

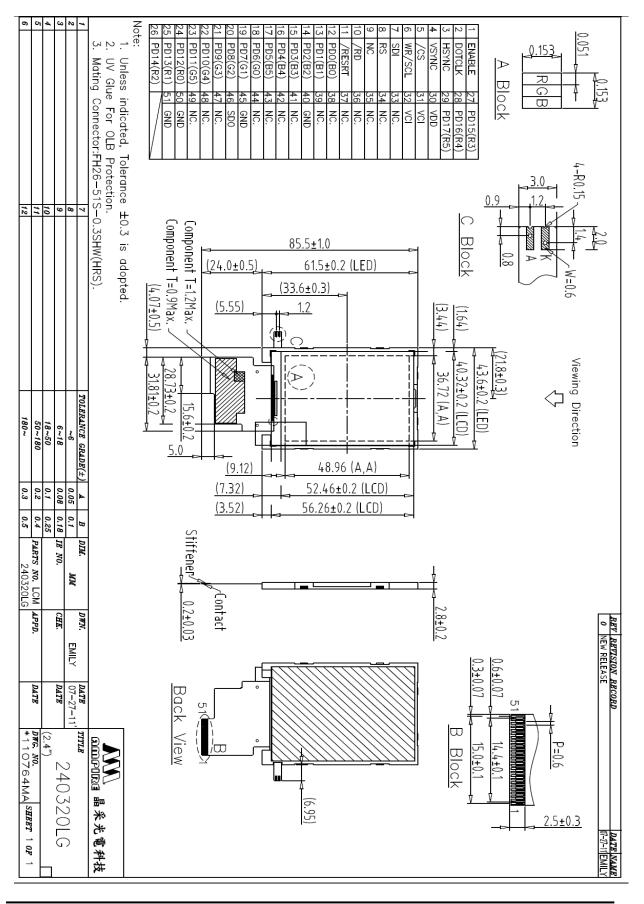

### 2 Mechanical specifications

### Dimensions and weight

| Item                      |                  | Specifications                 | Unit |

|---------------------------|------------------|--------------------------------|------|

| External shape dimensions |                  | *1 43.6 (W) x 85.5 (H) x2.8(T) | mm   |

| Main Pixel size           |                  | 0.153 (W) x 0.153 (H)          | mm   |

| LCD                       | Active area      | 36.72 (W) x 48.96 (H)          | mm   |

| 200                       | Number of Pixels | 240(H)x320(V) pixels           | mm   |

| Weight                    |                  | T.B.D.                         | g    |

\*1. This specification is about External shape on shipment from AMPIRE.

### 3 Absolute max. ratings and environment

3-1 Absolute max. ratings

Ta=25°C GND=0V

| Item          | Symbol        | Min. | Max. | Unit | Remarks                |

|---------------|---------------|------|------|------|------------------------|

| Power voltage | VDD – GND     | -0.3 | +4   | V    | Logic I/O power supply |

| Power voltage | VCI–GND       | -0.3 | +4   | V    | Driver power supply    |

| Power voltage | LED A – LED K | -0.5 | +15  | V    |                        |

### 3-2 Environment

| Item                     | Specifications          | Remarks                   |

|--------------------------|-------------------------|---------------------------|

| Storage temperature      | Max. +80 °C<br>Min30 °C | Note 1:<br>Non-condensing |

| Operating<br>temperature | Max. +70 °C<br>Min20 °C | Note 1:<br>Non-condensing |

Note 1 : Ta  $\leq$  +40 °C · · · Max.85%RH

Ta>+40  $^{o}\text{C}$  · · · The max. humidity should not exceed the humidity with 40  $^{o}\text{C}$  85%RH.

# 4 Electrical specifications

| 4-1 Electrical | characteristics of LCM |  |

|----------------|------------------------|--|

|----------------|------------------------|--|

(V<sub>DD</sub>=3.0V, Ta=25 °C)

| Item                       | Symbol              | Conditions              | MIN. | TYP. | MAX.               | Unit |

|----------------------------|---------------------|-------------------------|------|------|--------------------|------|

| IC power<br>voltage(Power) | $V_{DD}$            |                         | 2.3  | 2.8  | 3.3                | V    |

| IC power<br>voltage(Logic) | V <sub>CI</sub>     |                         | 2.3  | 2.8  | 3.3                | V    |

| High-level input voltage   | V <sub>IHC</sub>    |                         | 0.8  |      | $V_{DD}$           | V    |

| Low-level input voltage    | V <sub>ILC</sub>    |                         | -0.3 |      | $0.2V_{\text{DD}}$ | V    |

| Consumption current of VDD | I <sub>DD</sub>     | LED OFF                 | -    | 8    | 15                 | mA   |

| Consumption current of LED | I <sub>LED_ON</sub> | V <sub>LED</sub> =12.8V | -    | 20   | -                  | mA   |

※ 1. 1/320 duty.

### 4-2 LED back light specification

| Item                        | Symbol                           | Conditions           | MIN.      | TYP.       | MAX.         | Unit              |

|-----------------------------|----------------------------------|----------------------|-----------|------------|--------------|-------------------|

| Forward voltage             | V <sub>f</sub>                   | I <sub>f</sub> =20mA | 12.3      | 12.8       | 13.8         | V                 |

| Reverse voltage             | Vr                               |                      | -         | -          | 12           | V                 |

| Forward current             | l <sub>f</sub>                   | 4-chip serial        | -         | 18         | 20           | mA                |

| Power Consumption           | P <sub>BL</sub>                  | I <sub>f</sub> =20mA | -         | 256        | 276          | mW                |

| Uniformity (with L/G)       | -                                | l <sub>f</sub> =20mA | 80%*1     | -          | -            |                   |

| Bare LED Luminous intensity | V <sub>f</sub><br>I <sub>f</sub> | 13.2V<br>20mA        | 3700      | -          | -            | cd/m <sup>2</sup> |

| Luminous color              | White                            |                      |           |            |              |                   |

| Chip connection             | 4 chip serial connection         |                      |           |            |              |                   |

| LED life time               |                                  | 40K hr (E            | Estimated | data, Ta=2 | <b>25</b> ℃) |                   |

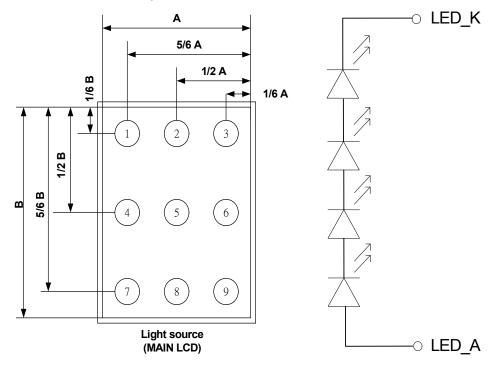

Bare LED measure position:

\*1 Uniformity (LT):  $\frac{Min(P1 \sim P9)}{Max(P1 \sim P9)} \times 100 \ge 80\%$

# 5 Main LCD

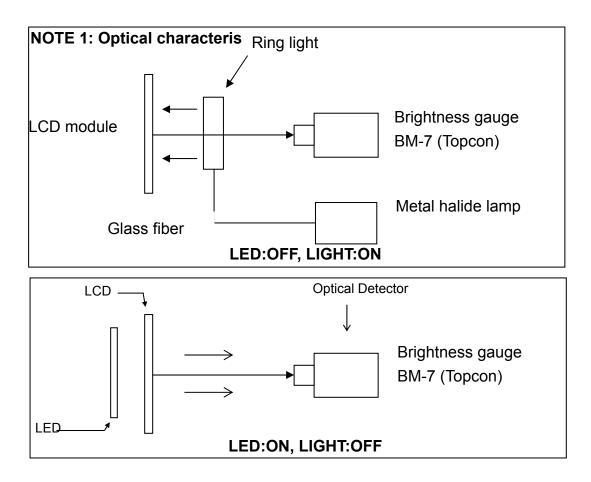

### 5-1 Optical characteristics

### (1/320 Duty in case except as specified elsewhere $Ta = 25^{\circ}C$ )

| Item                                    | Symbol | Temp. | Min.                       | Std. | Max.        | Unit                                               | Conditions                                                        |

|-----------------------------------------|--------|-------|----------------------------|------|-------------|----------------------------------------------------|-------------------------------------------------------------------|

| Response                                | Tr     | 25 °C |                            | 15   | 25          | me                                                 | θ=0 °°, φ=0 °                                                     |

| time                                    | Tf     | 25 °C |                            | 20   | 30          | ms                                                 | (Note 2)                                                          |

| Contrast ratio                          | CR     | 25 °C | -                          | 200  | -           | -                                                  | θ=0 <sup>°</sup> , φ=0 <sup>°</sup> LED:ON, LIGHT:OFF<br>(Note 4) |

| Transmittance                           | Т      | 25 °C | -                          | 4.7  | -           | %                                                  |                                                                   |

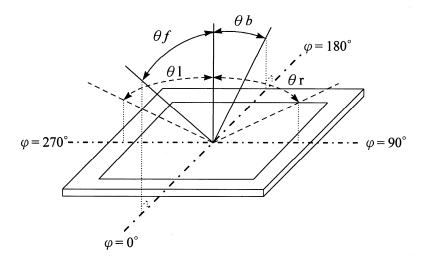

| Visual angle<br>range front<br>and rear | θ      | 25 °C | (θf) 35(20)<br>(θb) 65(45) |      |             | De-<br>gree                                        | φ= 0º, CR≧10 LED:ON LIGHT:OFF<br>(Note 3)                         |

| Visual angle<br>range left and<br>right | θ      | 25 °C | (θl) 70(45)<br>(θr) 70(45) |      | De-<br>gree | $\phi$ =90°, CR $\ge$ 10 LED:ON LIGHT:OFF (Note 3) |                                                                   |

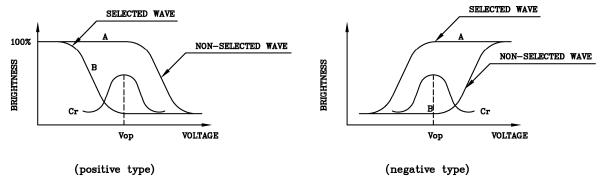

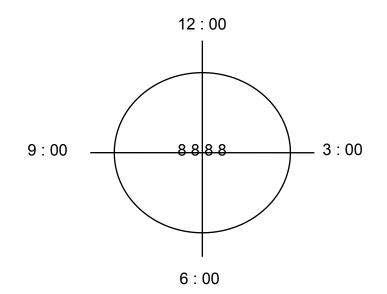

| Visual angle<br>direction<br>priority   |        |       | 12:00                      |      |             | (Note 5)                                           |                                                                   |

| Brightness                              |        |       | 250                        | 320  |             | cd/<br>m²                                          | $I_F$ =20mA, Full White pattern                                   |

5-2 CIE (x, y) chromaticity (1/320 Duty Ta =  $25^{\circ}$ C)

| Item   | Symbol | Т    | ransmissiv | Conditions |                                         |

|--------|--------|------|------------|------------|-----------------------------------------|

| nom    | Cymbol | Min. | Тур.       | Max.       | Conditions                              |

| Red    | Х      | 0.55 | 0.60       | 0.65       | θ=0°,φ=0°                               |

| Reu    | Y      | 0.28 | 0.33       | 0.38       | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |

| Green  | Х      | 0.30 | 0.35       | 0.40       | θ=0°,φ=0°                               |

| Oreen  | Y      | 0.53 | 0.58       | 0.63       |                                         |

| Blue   | Х      | 0.06 | 0.11       | 0.16       | θ=0°,φ=0°                               |

| Diue   | Y      | 0.03 | 0.08       | 0.13       | <i>/</i> 1                              |

| White  | Х      | 0.24 | 0.29       | 0.34       | θ=0°,φ=0°                               |

| vville | Y      | 0.29 | 0.34       | 0.39       | , T -                                   |

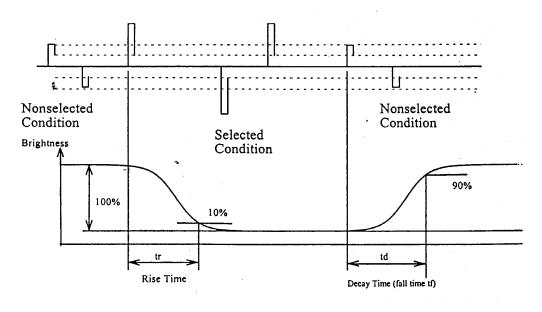

NOTE 2: Response tome definition

### NOTE 3: $\phi \ \circ \ \theta$ definition

Contrast Ratio : Cr=A/B

NOTE 5: Visual angle direction priority

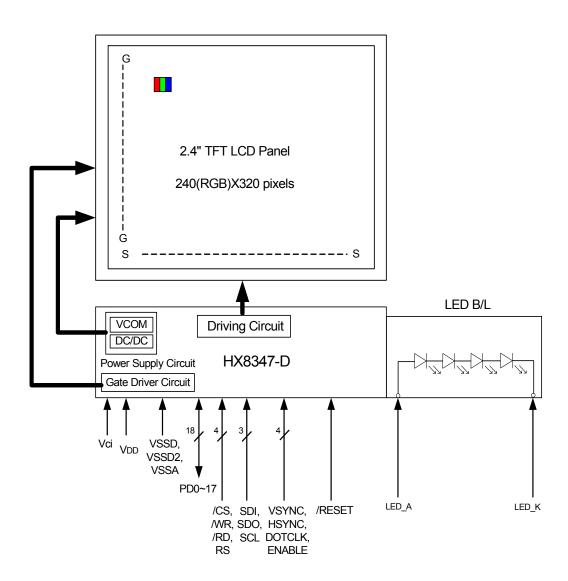

# 6 Block Diagram

### Block diagram (Main LCD)

Display format:A-Si TFT transmissive, Normally white type, 12 o'clock.Display composition:240 x RGB x 320 dotsLCD Driver :HX8347-D

# 7 Interface specifications

| Pin No.   | Terminal | Functions                                                                                                               |

|-----------|----------|-------------------------------------------------------------------------------------------------------------------------|

| 1         | ENABLE   | A data ENABLE signal in RGB I/F mode.                                                                                   |

| 2         | DOTCLK   | Dot clock signal in RGB I/F mode.                                                                                       |

| 3         | HSYNC    | Frame synchronizing signal in RGB I/F mode.                                                                             |

| 4         | VSYNC    | Frame synchronizing signal in RGB I/F mode.                                                                             |

| 5         | /CS      | Chip select signal.                                                                                                     |

| 6         | WR/SCL   | Write enable signal/Serial bus interface clock input pin.                                                               |

| 7         | SDI      | Serial bus interface data input/output pin.                                                                             |

| 8         | RS       | Command/display Data Selection.                                                                                         |

| 9         | NC       | NC                                                                                                                      |

| 10        | /RD      | Read enable signal.                                                                                                     |

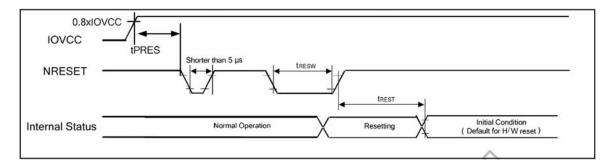

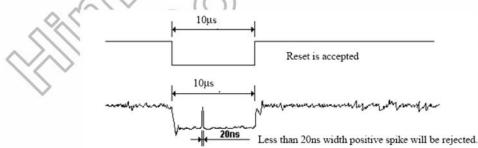

| 11        | /RESET   | Reset pin. Setting either pin low initializes the LSI.<br>Must be reset the chop after power being supplied.            |

| 12        | PD0      |                                                                                                                         |

| 13        | PD1      |                                                                                                                         |

| 14        | PD2      |                                                                                                                         |

| 15        | PD3      |                                                                                                                         |

| 16        | PD4      |                                                                                                                         |

| 17        | PD5      | Mode IM[3:0] PD Pin in use                                                                                              |

| 18        | PD6      | MCU 18-bit Type I         1000         PD [17:0]           MCU 16-bit Type I         0000         PD [15:10]            |

| 19        | PD7      | MCU 9-bit Type I 1001 PD [8:0]                                                                                          |

| 20        | PD8      | MCU 8-bit Type I 0001 PD [7:0]                                                                                          |

| 21        | PD9      | MCU 18-bit Type II         1010         PD [17:0]           MCU 16-bit Type II         0010         PD [17:10], DB[8:1] |

| 22        | PD10     | MCU 9-bit Type II 1011 PD [17:9]                                                                                        |

| 23        | PD11     | MCU 8-bit Type II 0011 PD [17:10]                                                                                       |

| 24        | PD12     | SDI, SDO, SCL                                                                                                           |

| 25        | PD13     | Serial Mode/Digital<br>RGB Interface Mode0100R[5:0]=PD[17:12]<br>G[5:0]=PD[11:6]                                        |

| 26        | PD14     | B[5:0]=PD[5:0]                                                                                                          |

| 27        | PD15     |                                                                                                                         |

| 28        | PD16     |                                                                                                                         |

| 29        | PD17     |                                                                                                                         |

| (To be co | ntinued) |                                                                                                                         |

(To be continued)

| 30 | VDD | Power supply for the internal logic circuit. (VDD=1.65~3.3V) |

|----|-----|--------------------------------------------------------------|

| 31 | VCI | Power supply for Stop up size (1/CI=2.2.2.2)                 |

| 32 | VCI | Power supply for Step-up circuit. (VCI=2.3~3.3V)             |

| 33 | NC  |                                                              |

| 34 | NC  |                                                              |

| 35 | NC  |                                                              |

| 36 | NC  | NC                                                           |

| 37 | NC  |                                                              |

| 38 | NC  |                                                              |

| 39 | NC  |                                                              |

| 40 | GND | GND-terminal                                                 |

| 41 | NC  |                                                              |

| 42 | NC  | NC                                                           |

| 43 | NC  | NC                                                           |

| 44 | NC  |                                                              |

| 45 | GND | GND-terminal                                                 |

| 46 | GND | GND-terminal                                                 |

| 47 | NC  |                                                              |

| 48 | NC  | NC                                                           |

| 49 | NC  |                                                              |

| 50 | GND | GND-terminal                                                 |

| 51 | GND |                                                              |

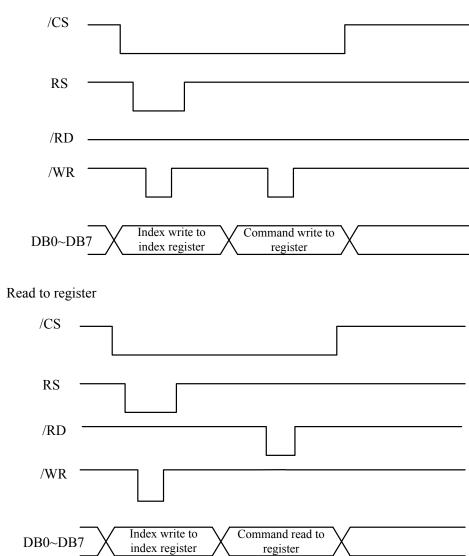

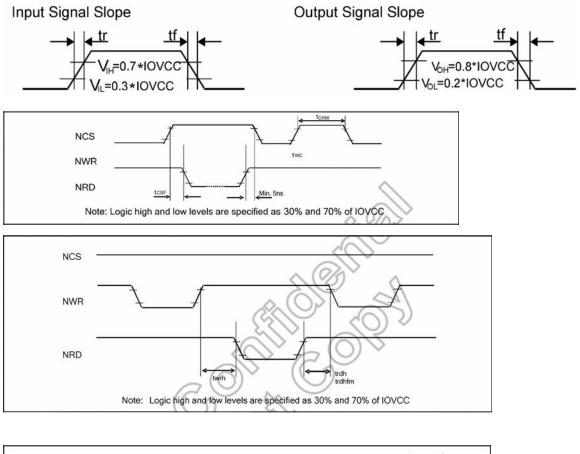

### 7-1 Parallel bus system interface

The input / output data from data pins (DB17-0) and signal operation of the I80 series parallel bus interface are listed as below.

| Operations                                     | WR/SCL | /RD | RS |

|------------------------------------------------|--------|-----|----|

| Writes Indexes into IR                         | 0      | 1   | 0  |

| Reads internal status                          | 1      | 0   | 0  |

| Writes command into register or data into GRAM | 0      | 1   | 1  |

| Reads command from register or data from GRAM  | 1      | 0   | 1  |

Write to register

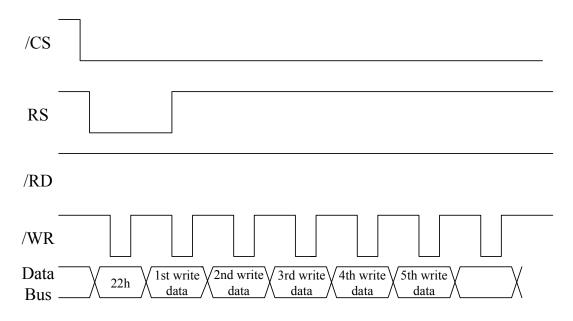

### Write to the graphic RAM

# Read to the graphic RAM

# 7-2 MCU data color coding

### MCU Data Color Coding for RAM data Write

| Register | DB17 | <b>DB16</b> | <b>DB15</b> | <b>DB14</b> | DB13 | <b>DB12</b> | DB11 | DB10 | DB9 | DB8 | DB7        | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 | Command                         |

|----------|------|-------------|-------------|-------------|------|-------------|------|------|-----|-----|------------|-----|-----|-----|-----|-----|-----|-----|---------------------------------|

| Command  | Х    | Х           | Х           | X           | х    | X           | X    | X    | ×   | х   | 0          | 0   | 1   | 0   | 0   | 0   | 1   | 0   | 22H                             |

| 17H      | DB17 | DB16        | DB15        | DB14        | DB13 | DB12        | DB11 | DB10 | DB9 | DB8 | DB7        | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DBO | Color                           |

|          | Х    | Х           | Х           | Х           | Х    | X           | Х    | Х    | Х   | Х   | R3         | R2  | R1  | RO  | G3  | G2  | G1  | G0  | 4K-Color                        |

| 03h      | Х    | Х           | Х           | Х           | Х    | Х           | х    | Х    | Х   | Х   | <b>B</b> 3 | B2  | B1  | BO  | R3  | R2  | R1  | RO  | (2-pixels/ 3-bytes              |

|          | Х    | Х           | Х           | Х           | Х    | X           | Х    | Х    | Х   | Х   | G3         | G2  | G1  | G0  | B3  | B2  | B1  | BO  | (2-pixels/ 0-bytes              |

| 05h      | Х    | Х           | Х           | Х           | Х    | Х           | Х    | Х    | Х   | Х   | R4         | R3  | R2  | R1  | RO  | G5  | G4  | G3  | 65K-Color                       |

| 0311     | Х    | х           | х           | X           | х    | ×           | Х    | х    | Х   | х   | G2         | G1  | G0  | B4  | B3  | B2  | B1  | BO  | (1-pixel/ 2-bytes               |

|          | Х    | Х           | Х           | Х           | Х    | Х           | Х    | Х    | Х   | Х   | R5         | R4  | R3  | R2  | R1  | RO  | х   | X   |                                 |

| 06h      | ×    | X           | X           | X           | X    | X           | X    | X    | х   | ×   | G5         | G4  | G3  | G2  | G1  | G0  | х   | ×   | 262K-Color<br>(1-pixel/ 3bytes) |

|          | x    | X           | X           | X           | X    | X           | Х    | X    | Х   | X   | B5         | B4  | B3  | B2  | B1  | BO  | х   | X   | (1-pixel/ obytes)               |

- Parallel 8-Bit Bus Interface typel (IM3,IM2,IM1,IM0="0001")

Table 5.3 8-bit parallel interface type I GRAM write table

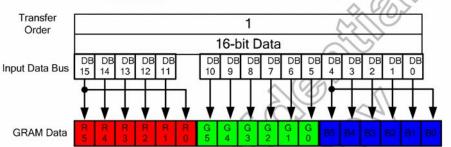

#### - Parallel 16-Bit Bus Interface typel (IM3,IM2,IM1,IM0="0000")

| Register | DB17 | <b>DB16</b> | <b>DB15</b> | DB14 | DB13 | <b>DB12</b> | <b>DB11</b> | <b>DB10</b> | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3 | DB2        | DB1 | DB0 | Command            |

|----------|------|-------------|-------------|------|------|-------------|-------------|-------------|-----|-----|-----|-----|-----|-----|-----|------------|-----|-----|--------------------|

| Command  | ×    | Х           | Х           | х    | X    | ×           | ×           | X           | Х   | Х   | 0   | 0   | 1   | 0   | 0   | 0          | 1   | 0   | 22H                |

| 17H      | DB17 | <b>DB16</b> | <b>DB15</b> | DB14 | DB13 | DB12        | <b>DB11</b> | DB10        | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3 | DB2        | DB1 | DB0 | Color              |

| 03h      |      |             |             |      |      |             | R3          | R2          | R1  | RO  | G3  | G2  | G1  | G0  | B3  | B2         | B1  | B0  | 4K-Color           |

| 05h      | Х    | Х           | R4          | R3   | R2   | R1          | RO          | G5          | G4  | G3  | G2  | G1  | G0  | B5  | B4  | <b>B</b> 3 | B2  | B1  | 65K-Color          |

|          | ×    | Х           | R5          | R4   | R3   | R2          | R1          | RO          | х   | х   | G5  | G4  | G3  | G2  | G1  | G0         | х   | х   | 262K-Color         |

| 06h      | ×    | Х           | B5          | B4   | B3   | B2          | B1          | BO          | х   | х   | R5  | R4  | R3  | R2  | R1  | RO         | х   | х   | (2-pixels/ 3bytes) |

|          | Х    | х           | G5          | G4   | G3   | G2          | G1          | GO          | x   | х   | B5  | B4  | B3  | B2  | B1  | BO         | х   | х   |                    |

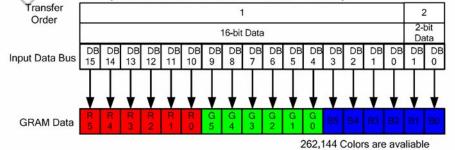

| 07h      | X    | Х           | R5          | R4   | R3   | R2          | R1          | RO          | G5  | G4  | G3  | G2  | G1  | G0  | B5  | B4         | B3  | B2  | 262K-Color (16+2   |

| UNI      | X    | X           | х           | X    | X    | X           | x           | x           | х   | х   | х   | X   | X   | х   | Х   | х          | B1  | BO  | 20211-00101 (10+2  |

Table 5.4 16-bit parallel interface type I GRAM write table

#### - Parallel 9-Bit Bus Interface typel (IM3,IM2,IM1,IM0="1001")

| Register | DB17 | DB16 | DB15        | DB14 | DB13 | DB12        | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 | Register           |

|----------|------|------|-------------|------|------|-------------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|--------------------|

| Command  | Х    | X    | Х           | X    | х    | Х           | X    | Х    | Х   | X   | 0   | 0   | 1   | 0   | 0   | 0   | 1   | 0   | 22H                |

| 17H      | DB17 | DB16 | <b>DB15</b> | DB14 | DB13 | <b>DB12</b> | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 | Color              |

| 06h      | Х    | X    | Х           | X    | Х    | Х           | Х    | X    | х   | R5  | R4  | R3  | R2  | R1  | RO  | G5  | G4  | G3  | 262K-Color         |

| 0011     | ×    | X    | х           | X    | X    | Х           | х    | х    | х   | G2  | G1  | G0  | B5  | B4  | B3  | B2  | B1  | B0  | (1-pixels/ 2bytes) |

Table 5.5 9-bit parallel interface type I GRAM write table

#### - Parallel 18-Bit Bus Interface typel (IM3,IM2,IM1,IM0="1000")

| Register | <b>DB17</b> | <b>DB16</b> | <b>DB15</b> | <b>DB14</b> | DB13 | <b>DB12</b> | <b>DB11</b> | <b>DB10</b> | DB9 | DB8 | DB7 | DB6 | DB5 | DB4        | DB3 | DB2 | DB1 | DB0 | Register   |

|----------|-------------|-------------|-------------|-------------|------|-------------|-------------|-------------|-----|-----|-----|-----|-----|------------|-----|-----|-----|-----|------------|

| Command  | х           | x           | х           | x           | х    | x           | x           | х           | х   | x   | 0   | 0   | 1   | 0          | 0   | 0   | 1   | 0   | 22H        |

| 17H      | DB17        | DB16        | <b>DB15</b> | DB14        | DB13 | DB12        | DB11        | DB10        | DB9 | DB8 | DB7 | DB6 | DB5 | DB4        | DB3 | DB2 | DB1 | DB0 | Color      |

| 06h      | R5          | R4          | R3          | R2          | R1   | RO          | G5          | G4          | G3  | G2  | G1  | GO  | B5  | <b>B</b> 4 | B3  | B2  | B1  | BO  | 262K-Color |

Table 5.6 18-bit parallel interface type I GRAM write table

#### - Parallel 8-Bit Bus Interface typeII (IM3,IM2,IM1,IM0="0011")

| Register | <b>DB17</b> | <b>DB16</b> | <b>DB15</b> | <b>DB14</b> | DB13 | <b>DB12</b> | <b>DB11</b> | <b>DB10</b> | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 | Command                         |

|----------|-------------|-------------|-------------|-------------|------|-------------|-------------|-------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|---------------------------------|

| Command  | 0           | 0           | 1           | 0           | 0    | 0           | 1           | 0           | X   | Х   | х   | x   | Х   | Х   | Х   | Х   | Х   | Х   | 22H                             |

| 17H      | <b>DB17</b> | DB16        | DB15        | <b>DB14</b> | DB13 | DB12        | DB11        | DB10        | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 | Color                           |

|          | R3          | R2          | R1          | RO          | G3   | G2          | G1          | G0          | X   | ×   | x   | x   | х   | х   | х   | х   | ×   | х   | dif Onlar                       |

| 03h      | B3          | B2          | B1          | BO          | R3   | R2          | R1          | RO          | Х   | х   | х   | Х   | х   | X   | Х   | X   | Х   | х   | 4K-Color<br>(2-pixels/ 3-bytes) |

|          | G3          | G2          | G1          | GO          | B3   | B2          | B1          | BO          | X   | х   | x   | x   | Х   | X   | X   | Х   | X   | Х   | (2-pixels/ 0-bytes              |

| 05h      | R4          | R3          | R2          | R1          | RO   | G5          | G4          | G3          | Х   | Х   | X   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | 65K-Color                       |

| 0511     | G2          | G1          | G0          | B4          | B3   | B2          | B1          | BO          | х   | X   | x   | x   | х   | X   | Х   | х   | х   | х   | (1-pixel/ 2-bytes)              |

|          | R5          | R4          | R3          | R2          | R1   | RO          | х           | X           | Х   | Х   | Х   | Х   | X   | Х   | Х   | Х   | Х   | Х   | 0001/ 0-1                       |

| 06h      | G5          | G4          | G3          | G2          | G1   | G0          | х           | x           | X   | х   | x   | x   | х   | X   | X   | X   | X   | X   | 262K-Color<br>(1-pixel/ 3bytes) |

|          | B5          | B4          | B3          | B2          | B1   | BO          | х           | x           | X   | х   | X   | X   | Х   | X   | х   | х   | X   | Х   | (1-pixel/ Suyles)               |

Table 5.7 8-bit parallel interface type II GRAM write table

#### - Parallel 16-Bit Bus Interface typeII (IM3,IM2,IM1,IM0="0010")

| Register | <b>DB17</b> | <b>DB16</b> | DB15 | DB14 | DB13 | DB12 | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 | Command                          |

|----------|-------------|-------------|------|------|------|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----------------------------------|

| Command  |             |             |      |      |      |      |      |      | Х   | 0   | 0   | 1   | 0   | 0   | 0   | 1   | 0   | ×   | 22H                              |

| 17H      | <b>DB17</b> | DB16        | DB15 | DB14 | DB13 | DB12 | DB11 | DB10 | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DBO | Color                            |

| 03h      | X           | х           | X    | x    | R3   | R2   | R1   | RO   | x   | G3  | G2  | G1  | GO  | B3  | B2  | B1  | BO  | х   | 4K-Color                         |

| 05h      | R4          | R3          | R2   | R1   | RO   | G5   | G4   | G3   | х   | G2  | G1  | G0  | B4  | B3  | B2  | B1  | BO  | х   | 65K-Color                        |

|          | R5          | R4          | R3   | R2   | R1   | RO   | х    | X    | х   | G5  | G4  | G3  | G2  | G1  | G0  | х   | х   | х   | 0001/ 0-1                        |

| 06h      | B5          | B4          | B3   | B2   | B1   | BO   | х    | x    | х   | R5  | R4  | R3  | R2  | R1  | RO  | х   | x   | х   | 262K-Color<br>(2-pixels/ 3bytes) |

|          | G5          | G4          | G3   | G2   | G1   | GO   | х    | x    | х   | B5  | B4  | B3  | B2  | B1  | BO  | x   | x   | х   | (2-pixels/ obytes)               |

| 07h      | R5          | R4          | R3   | R2   | R1   | RO   | G5   | G4   | х   | G3  | G2  | G1  | G0  | B5  | B4  | B3  | B2  | х   | 262K-Color (16+2                 |

| 0/11     | B1          | BO          | x    | x    | x    | x    | x    | x    | x   | х   | x   | x   | x   |     |     | x   | X   | x   | 2021-00101 (10+2                 |

Table 5.8 16-bit parallel interface type II GRAM write set table

- Parallel 9-Bit Bus Interface typell (IM3,IM2,IM1,IM0="1011")

| i araner e | 0   |     |     |     | .) P |     |     |     |    | 0  |    | 1.11 | 0  |    |    |    |    |    |                   |

|------------|-----|-----|-----|-----|------|-----|-----|-----|----|----|----|------|----|----|----|----|----|----|-------------------|

| Register   | D17 | D16 | D15 | D14 | D13  | D12 | D11 | D10 | D9 | D8 | D7 | D6   | D5 | D4 | D3 | D2 | D1 | DO | Register          |

| Command    | 0   | 0   | 1   | 0   | 0    | 0   | 1   | 0   | х  | х  | х  | x    | x  | х  | X  | x  | х  | х  | 22H               |

| 17H        | D8  | D7  | D6  | D5  | D4   | D3  | D2  | D1  | DO | D8 | D7 | D6   | D5 | D4 | D3 | D2 | D1 | DO | Color             |

| 06h        | R5  | R4  | R3  | R2  | R1   | RO  | G5  | G4  | G3 | х  | X  | X    | X  | х  | X  | X  | X  | X  | 262K-Color        |

| 0011       | G2  | G1  | G0  | B5  | B4   | B3  | B2  | B1  | BO | х  | x  | x    | x  | x  | x  | x  | x  | x  | (1-pixel/ 2bytes) |

|            |     |     |     | -   | _    | _   |     |     | _  | _  | _  | _    |    | _  | -  |    | _  | _  |                   |

Table 5.9 9-bit parallel interface set type II GRAM write table

#### - Parallel 18-Bit Bus Interface typeII (IM3,IM2,IM1,IM0="1010")

| Register | DB17 | DB16        | DB15       | DB14 | DB13 | DB12        | DB11        | <b>DB10</b> | DB9 | DB8 | DB7 | DB6 | DB5        | DB4 | DB3 | DB2 | DB1 | DB0 | Register   |

|----------|------|-------------|------------|------|------|-------------|-------------|-------------|-----|-----|-----|-----|------------|-----|-----|-----|-----|-----|------------|

| Command  | Х    | x           | х          | х    | х    | х           | х           | x           | х   | 0   | 0   | 1   | 0          | 0   | 0   | 1   | 0   | х   | 22H        |

| 17H      | DB17 | <b>DB16</b> | DB15       | DB14 | DB13 | <b>DB12</b> | <b>DB11</b> | <b>DB10</b> | DB9 | DB8 | DB7 | DB6 | DB5        | DB4 | DB3 | DB2 | DB1 | DB0 | Color      |

| 06h      | R5   | R4          | <b>R</b> 3 | R2   | R1   | RO          | G5          | G4          | G3  | G2  | G1  | GO  | <b>B</b> 5 | B4  | B3  | B2  | B1  | BO  | 262K-Color |

Table 5.10 18-bit parallel interface type II GRAM write set table

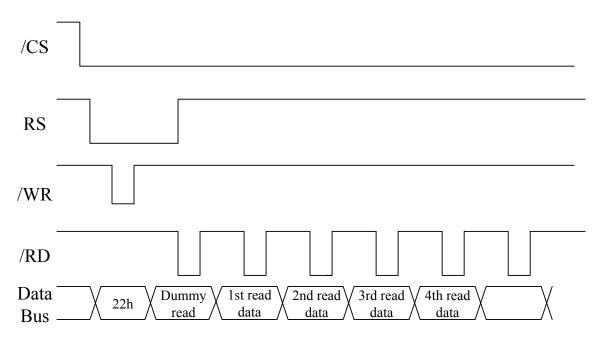

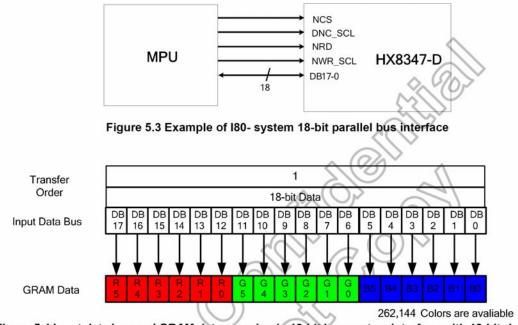

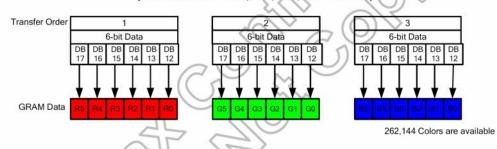

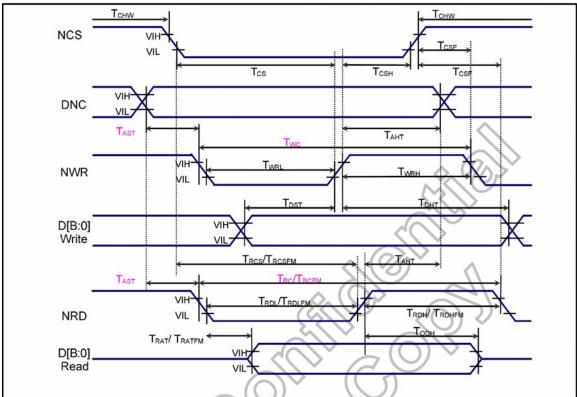

### 7-3 80-system 18-bit interface

The I80-system 18-bit parallel bus interface **type I** in command-parameter interface mode can be used by setting external pins "IM3, IM2, IM1, IM0" pins to "1000". And the I80-system 18-bit parallel bus interface **type II** in

command-parameter interface mode can be used by setting ""IM3, IM2, IM1, and IM0"pins to "1010". Figure 5.3 is the example of interface with I80 microcomputer system interface.

Figure 5.4 Input data bus and GRAM data mapping in 18-bit bus system interface with 18-bit-data Input ("IM3, IM2, IM1, IM"="1010" or "1000")

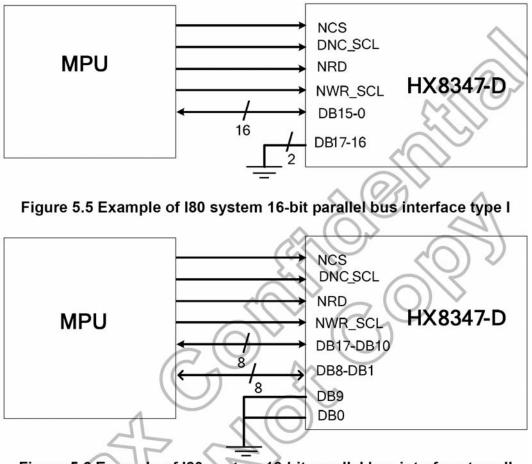

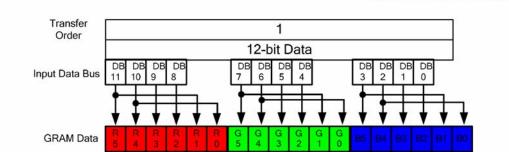

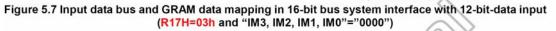

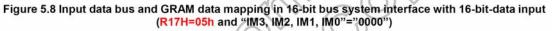

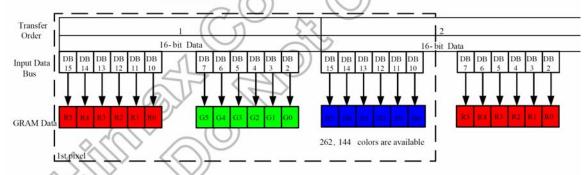

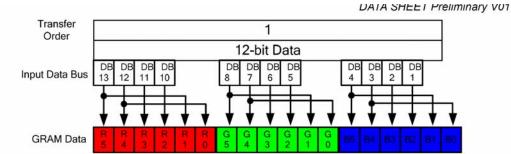

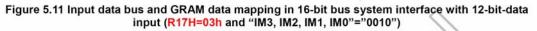

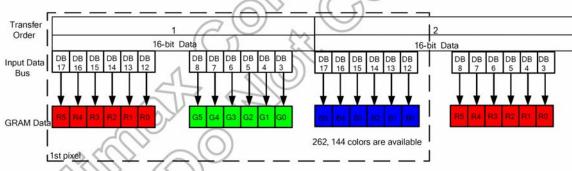

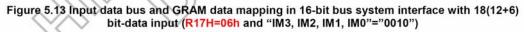

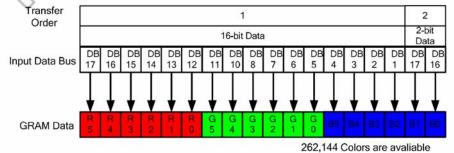

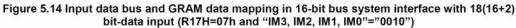

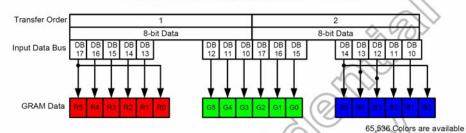

# 7-4 80-system 16-bit interface

The I80-system 16-bit parallel bus interface **type I** in command-parameter interface mode can be used by setting external pins ""IM3, IM2, IM1, IM0" pins to "0000". And I80-system 16-bit parallel bus interface **type II** in command-parameter interface mode can be used by setting ""IM3, IM2, IM1, IM0" pins to "0010". Figure 5.5 is the example of type I interface with I80 microcomputer system interface. And Figure 5.6 is the example of type II interface with I80 microcomputer system interface.

Figure 5.6 Example of I80 system 16-bit parallel bus interface type II

65,536 Colors are avaliable

65,536 Colors are avaliable

Figure 5.9 Input data bus and GRAM data mapping in 16-bit bus system interface with 18 bit-data input (R17H=06h and "IM3, IM2, IM1, IM0"="0000")

65,536 Colors are avaliable

65,536 Colors are avaliable

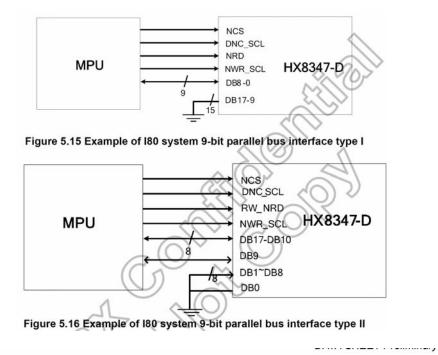

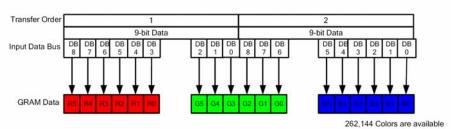

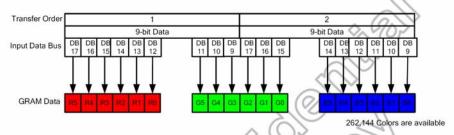

### 7-5 9-bit parallel bus system interface

The I80-system 9-bit parallel bus interface **type I** in command-parameter interface mode can be used by setting external pins ""IM3, IM2, IM1, IM0" pins to "1001". And I80-system 9-bit parallel bus interface **type II** in command-parameter interface mode can be used by setting ""IM3, IM2, IM1, IM0" pins to "1011". Figure 5.15 is the example of type I interface with I80 microcomputer system interface. And Figure 5.16 is the example of type II interface with I80 microcomputer system interface.

Figure 5.17 Input data bus and GRAM data mapping in 9-bit bus system interface with 18-bit-data input (R17H=06h and "IM3, IM2, IM1, IM0"="1001")

Figure 5.18 Input data bus and GRAM data mapping in 9-bit bus system interface with 18-bit-data input (R17H=06h and "IM3, IM2, IM1, IM0"="1011")

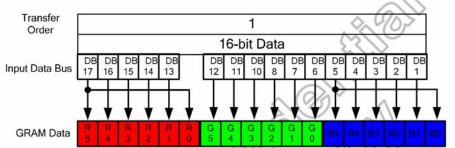

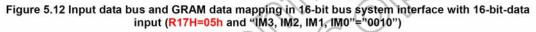

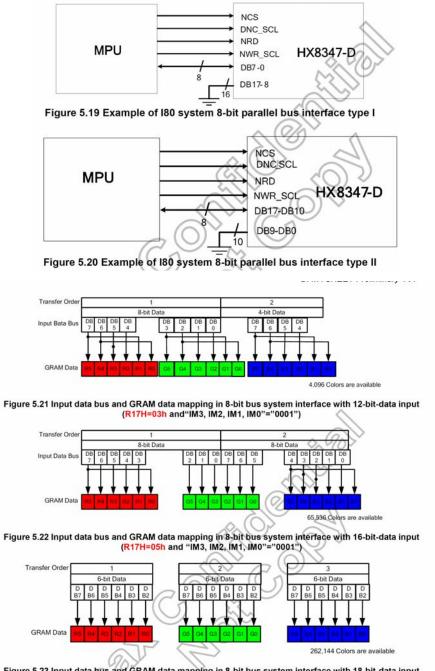

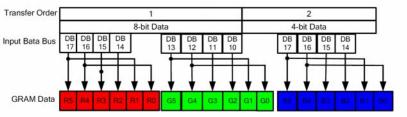

### 7-6 8-bit Parallel Bus System Interface

The I80-system 8-bit parallel bus interface **type I** in command-parameter interface mode can be used by setting external pins ""IM3, IM2, IM1, IM0" pins to "0001". And I80-system 8-bit parallel bus interface **type II** in command-parameter interface mode can be used by setting ""IM3, IM2, IM1, IM0" pins to "0011". Figure 5.19 is the example of type I interface with I80 microcomputer system interface. And Figure 5.20 is the example of type II interface with I80 microcomputer system interface.

DATA SHEET Preliminary V01

4,096 Colors are available

Figure 5.24 Input data bus and GRAM data mapping in 8-bit bus system interface with 12-bit-data input (R17H=03h and"IM3, IM2, IM1, IM0"="0011")

Figure 5.25 Input data bus and GRAM data mapping in 8-bit bus system interface with 16-bit-data input (R17H=05h and "IM3, IM2, IM1, IM0"="0011")

Figure 5.26 Input data bus and GRAM data mapping in 8-bit bus system interface with 18-bit-data input (R17H=06h and "IM3, IM2, IM1, IM0"="0011")

### 7-7 MCU Data Color Coding for RAM data Read

| i aranor e          |     |     |     |     | -21- |     |     |     |    |    |    | ,  |    |    |    |    |    |    |                                 |

|---------------------|-----|-----|-----|-----|------|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|---------------------------------|

| Register            | D17 | D16 | D15 | D14 | D13  | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | DO | Command                         |

| Command             | X   | х   | X   | ×   | Х    | Х   | Х   | Х   | Х  | X  | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 0  | 22H                             |

|                     | D17 | D16 | D15 | D14 | D13  | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | DO | Color                           |

| Deed                | х   | х   | х   | X   | X    | х   | х   | х   | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Dummy Read                      |

| Read<br>Data Format | Х   | Х   | Х   | Х   | Х    | Х   | Х   | Х   | Х  | Х  | R5 | R4 | R3 | R2 | R1 | RO | х  | х  |                                 |

| Bataronnat          | ×   | х   | ×   | ×   | ×    | ×   | X   | ×   | Х  | X  | G5 | G4 | G3 | G2 | G1 | GO | х  | х  | 262K-Color<br>(1-pixel/ 3bytes) |

|                     | х   | Х   | х   | Х   | х    | х   | Х   | Х   | Х  | Х  | B5 | B4 | B3 | B2 | B1 | BO | х  | х  | (1-pixel/ obytes)               |

- Parallel 8-Bit Bus Interface type I (IM3,IM2,IM1,IM0="0001")

Table 5.11 8-bit parallel interface type I GRAM read table

- Parallel 16-Bit Bus Interface type I (IM3,IM2,IM1,IM0="0000")

| Register            | D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | DO | Command            |

|---------------------|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|--------------------|

| Command             | Х   | Х   | X   | Х   | Х   | X   | X   | Х   | Х  | X  | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 0  | 22H                |

|                     | D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | DO | Color              |

| Deed                | х   | x   | х   | x   | x   | x   | x   | x   | X  | X  | Х  | Х  | ×  | Х  | Х  | Х  | Х  | Х  | Dummy Read         |

| Read<br>Data Format | Х   | X   | R5  | R4  | R3  | R2  | R1  | RO  | х  | X  | G5 | G4 | G3 | G2 | G1 | G0 | х  | х  | 262K-Color         |

| Data i officiat     | Х   | ×   | B5  | B4  | B3  | B2  | B1  | B0  | х  | x  | R5 | R4 | R3 | R2 | R1 | RO | х  | x  | (2-pixels/ 3bytes) |

|                     | X   | Х   | G5  | G4  | G3  | G2  | G1  | G0  | х  | x  | B5 | B4 | B3 | B2 | B1 | BO | х  | x  | (2-pixel3/ obytes) |

Table 5.12 16-bit parallel interface type I GRAM read table

#### - Parallel 9-Bit Bus Interface type I (IM3,IM2,IM1,IM0="1001"))

| Register    | D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | DO | Register          |

|-------------|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|-------------------|

| Command     | Х   | Х   | Х   | X   | X   | Х   | Х   | Х   | Х  | Х  | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 0  | 22H               |

|             | D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | DO | Color             |

| Read        | х   | x   | х   | x   | x   | х   | х   | x   | Х  | ×  | ×  | X  | х  | X  | X  | Х  | ×  | X  | Dummy Read        |

| Data Format | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | х  | R5 | R4 | R3 | R2 | R1 | RO | G5 | G4 | G3 | 262K-Color        |

|             | х   | х   | х   | X   | X   | X   | х   | Х   | x  | G2 | G1 | G0 | B5 | B4 | B3 | B2 | B1 | B0 | (1-pixel/ 2bytes) |

Table 5.13 9-bit parallel interface type I GRAM read table

#### - Parallel 18-Bit Bus Interface type I (IM3,IM2,IM1,IM0="1000")

| Register            | D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | DO | Register   |

|---------------------|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|------------|

| Command             | х   | х   | х   | х   | х   | х   | х   | х   | х  | х  | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 0  | 22H        |

| Dead                | D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | DO | Color      |

| Read<br>Data Format | х   | х   | х   | х   | х   | х   | х   | х   | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Dummy Read |

| Data i Officiat     | R5  | R4  | R3  | R2  | R1  | RO  | G5  | G4  | G3 | G2 | G1 | G0 | B5 | B4 | B3 | B2 | B1 | BO | 262K-Color |

Table 5.14 18-bit parallel interface type I GRAM read table

#### - Parallel 8-Bit Bus Interface type II (IM3,IM2,IM1,IM0="0011")

| Register            | <b>DB17</b> | <b>DB16</b> | <b>DB15</b> | <b>DB14</b> | DB13 | <b>DB12</b> | DB11 | <b>DB10</b> | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 | Command                         |

|---------------------|-------------|-------------|-------------|-------------|------|-------------|------|-------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|---------------------------------|

| Command             | 0           | 0           | 1           | 0           | 0    | 0           | 1    | 0           | Х   | Х   | х   | х   | Х   | Х   | X   | Х   | Х   | Х   | 22H                             |

|                     | DB17        | DB16        | DB15        | DB14        | DB13 | <b>DB12</b> | DB11 | DB10        | DB9 | DB8 | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 | Color                           |

| Read<br>Data Format | х           | X           | х           | х           | x    | x           | x    | X           | Х   | х   | Х   | Х   | X   | Х   | х   | Х   | Х   | Х   | Dummy Read                      |

|                     | R5          | R4          | R3          | R2          | R1   | RO          | х    | x           |     | 1   |     |     |     |     |     |     |     |     | 00014 0 1                       |

|                     | G5          | G4          | G3          | G2          | G1   | G0          | x    | x           | х   | х   | x   | x   | X   | х   | х   | х   | Х   | X   | 262K-Color<br>(1-pixel/ 3bytes) |

|                     | B5          | B4          | B3          | B2          | B1   | BO          | х    | X           | х   | X   | Х   | Х   | X   | х   | Х   | Х   | X   | Х   | (1-pixel/ Suyles)               |

Table 5.15 8-bit parallel interface type II GRAM read table

- Parallel 16-Bit Bus Interface type II (IM3,IM2,IM1,IM0="0010")

| Register            | <b>DB17</b> | DB16        | <b>DB15</b> | DB14        | DB13        | <b>DB12</b> | <b>DB11</b> | <b>DB10</b> | DB9 | DB8 | DB7 | DB6        | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 | Command                          |

|---------------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-----|-----|-----|------------|-----|-----|-----|-----|-----|-----|----------------------------------|

| Command             | х           | x           | х           | х           | x           | х           | x           | x           | х   | 0   | 0   | 1          | 0   | 0   | 0   | 1   | 0   | Х   | 22H                              |

|                     | DB17        | <b>DB16</b> | <b>DB15</b> | <b>DB14</b> | <b>DB13</b> | <b>DB12</b> | <b>DB11</b> | <b>DB10</b> | DB9 | DB8 | DB7 | DB6        | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 | Color                            |

| Dead                |             | х           | х           | х           | х           | х           | x           | х           | Х   |     | х   | х          | х   | х   | х   | х   | х   | Х   | Dummy Read                       |

| Read<br>Data Format | R5          | R4          | R3          | R2          | R1          | RO          | х           | x           | Х   | G5  | G4  | G3         | G2  | G1  | G0  | х   | х   | Х   |                                  |

| Data Format         | B5          | B4          | <b>B</b> 3  | B2          | B1          | BO          | х           | x           | ×   | R5  | R4  | R3         | R2  | R1  | RO  | х   | х   | х   | 262K-Color<br>(2-pixels/ 3bytes) |

|                     | G5          | G4          | G3          | G2          | G1          | G0          | х           | x           | ×   | B5  | B4  | <b>B</b> 3 | B2  | B1  | BO  | х   | x   | х   | (2-pixels/ obytes)               |

Table 5.16 16-bit parallel interface type II GRAM read table

# - Parallel 9-Bit Bus Interface type II (IM3,IM2,IM1,IM0="1011")

| Register    | D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | DO | Register          |

|-------------|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|-------------------|

| Command     | 0   | 0   | 1   | 0   | 0   | 0   | 1   | 0   | Х  | X  | X  | X  | X  | X  | X  | X  | X  | Х  | 22H               |

|             | D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | DO | Color             |

| Read        | х   | x   | х   | x   | x   | x   | x   | x   | X  | ×  | X  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Dummy Read        |

| Data Format | R5  | R4  | R3  | R2  | R1  | RO  | G5  | G4  | G3 | х  | Х  | X  | X  | X  | Х  | Х  | Х  | Х  | 262K-Color        |

|             | G2  | G1  | GO  | B5  | B4  | B3  | B2  | B1  | BO | х  | х  | X  | х  | х  | X  | Х  | X  | х  | (1-pixel/ 2bytes) |

Table 5.17 9-bit parallel interface type II GRAM read table

#### - Parallel 18-Bit Bus Interface type II (IM3,IM2,IM1,IM0="1010")

| Register            | D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | DO | Register   |

|---------------------|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|------------|

| Command             | х   | х   | х   | х   | x   | х   | X   | X   | х  | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 0  | Х  | 22H        |

| Dead                | D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | DO | Color      |

| Read<br>Data Format | х   | х   | х   | х   | х   | х   | х   | х   | Х  | Х  | Х  | Х  | Х  | Х  | X  | Х  | Х  | Х  | Dummy Read |

| Data i officiat     | R5  | R4  | R3  | R2  | R1  | RO  | G5  | G4  | G3 | G2 | G1 | GO | B5 | B4 | B3 | B2 | B1 | BO | 262K-Color |

Table 5.18 18-bit parallel interface type II GRAM read table

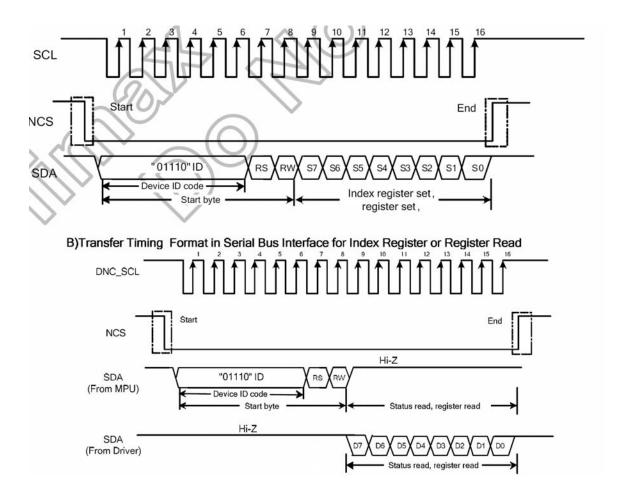

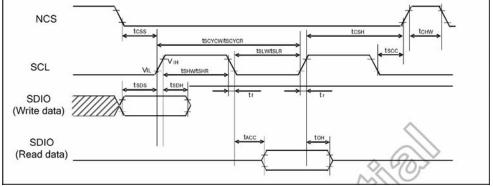

# 7-8 Serial bus system interface

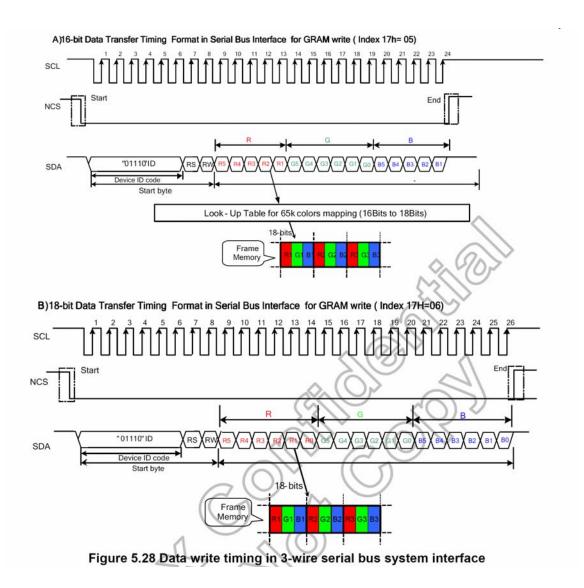

The HX8347-D supports two kinds of serial bus interface in register-content mode by setting external pins "IM2, IM1" pins to "10" 3-wire serial interface and "IM2, IM1" pins to "11" 4-wire serial interface. The serial bus system interface mode is enabled through the chip select line (/CS), and it is accessed via a control consisting of the serial input data (SDA), and the serial transfer clock signal (WR/SCL).

# 7-8-1 3-wire serial interface

As the chip select signal (NCS) goes low, the start byte needs to be transferred first. The start byte is made up of 6-bit bus device identification code; register select (RS) bit and read/write operation (RW) bit. The five upper bits of 6-bit bus device identification code must be set to "01110", and the least significant bit of the identification code must be set as the external pin IM0 input as "ID". The seventh bit (RS) of the start byte determines internal index register or register, GRAM accessing. RS must be set to "0" when writing data to the index register or reading the status and it must be set to "1" when writing or reading a command or GRAM data. The read or write operation is selected by the eighth bit (RW) of the start byte. The data is written to the chip when R/W = 0, and read from chip when RW = 1.

| RS | R/W | Function                              |

|----|-----|---------------------------------------|

| 0  | 0   | Set index register                    |

| 1  | 0   | Writes Instruction or GRAM data       |

| 1  | 1   | Reads command (Not support GRAM read) |

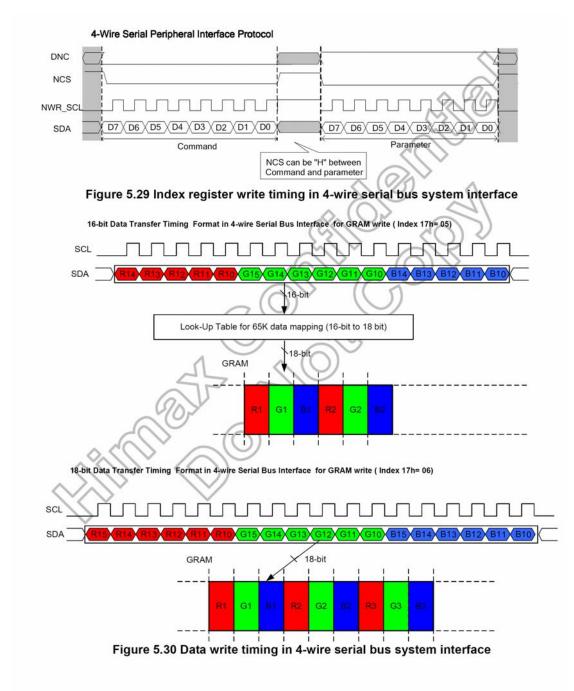

### 7-8-2 4-wire serial interface

4-pin serial case, data packet contains just transmission byte and control bit DNC is transferred by DNC pin. If DNC is low, the transmission byte is command byte. If DNC is high, the transmission byte is stored to index register or GRAM. The MSB is transmitted first. The serial interface is initialized when NCS is high. In this state, NWR\_SCL clock pulse or SDA data have no effect. A falling edge on NCS enables the serial interface and indicates the start of data transmission.

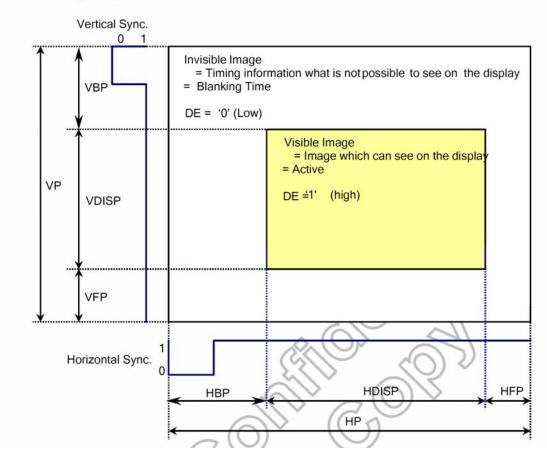

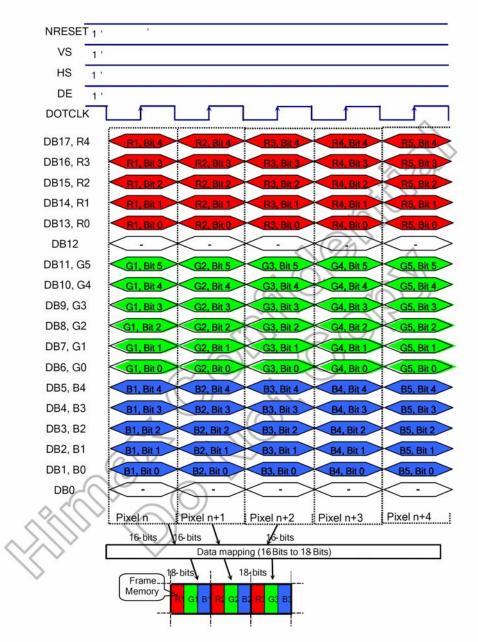

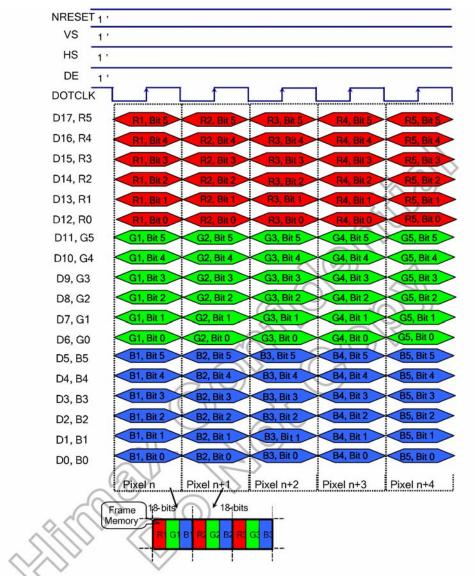

### 7-9 RGB Interface

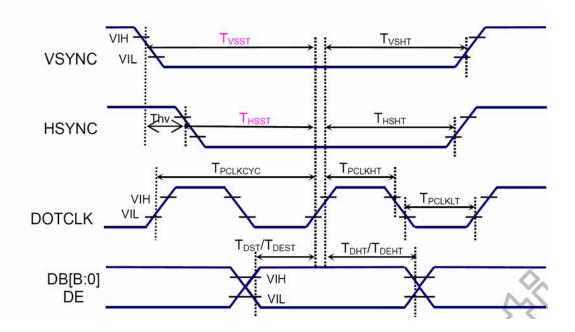

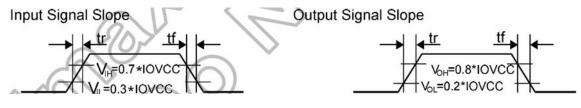

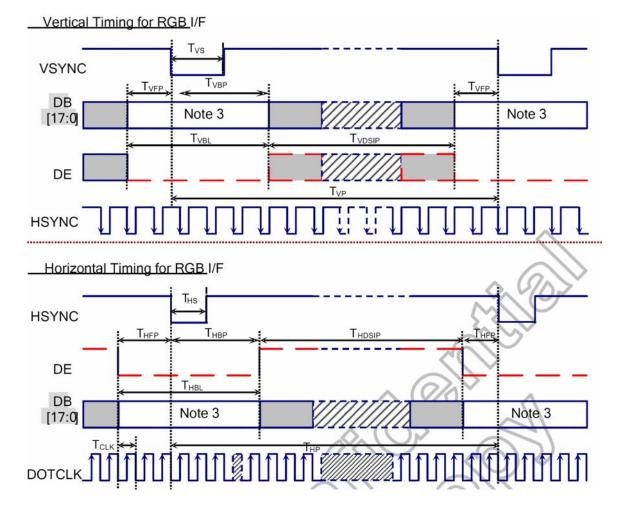

The HX8347-D uses RCM [1:0] ='10' or '11' hardware setting to select RGB interface. After Power on Sequence, the RGB interface is activated. When RCM [1:0] ='10' use VSYNC, HSYNC, DE, DOTCLK, DB17-0 parallel lines for the RGB interface (RGB mode 1). When RCM [1:0] ='11' use VSYNC, HSYNC, DOTCLK, DB17-0 parallel lines for the RGB interface (RGB mode 2).

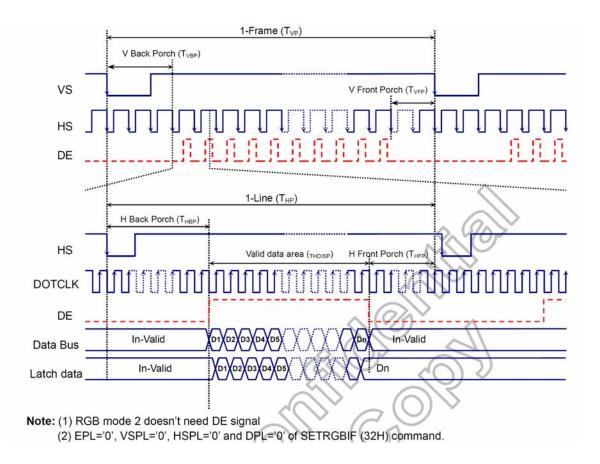

Pixel clock (DOTCLK) must be running all the time without stopping and it is used to entering VSYNC, HSYNC, DE and DB17-0 lines states when there is a rising edge of the DOTCLK.

In RGB interface mode 1, the valid display data is inputted in pixel unit via DB17-0 according to the high-level('H') of DE signal, and display operations are executed in synchronization with the frame synchronizing signal (VSYNC), line synchronizing signal (HSYNC) and pixel clock (DOTCLK). In RGB interface mode 2, the valid display data is inputted in pixel unit via DB17-0 according to the HBP setting of HSYNC signal, and the VBP setting of VSYNC. In these two RGB interface modes, the input display data is not written to GRAM and is displayed directly.

Vertical synchronization (VSYNC) signal is used to tell when there a new frame of the display is received, and this is negative ('-', '0', low) active. Horizontal synchronization signal (HSYNC) is used to tell when a new line of the frame is received, and this is negative ('-', '0', low) active. Data enable (DE) is used to tell when RGB information is received that should be transferred on the display, and this is positive ('+', '1', high) active. DB17-0 are used to tell what the information of the image is, that is transferred on the display when DE='H'.

DOTCL VSYNC HSYNC DE DB17-0

The pixel clock cycle is described in the following figure.

General timing diagram in RGB interface is as follow.

The image information is correct on the display when the timings are in range on the interface. However, the image information will be incorrect on the display, when timings are out of the range on the RGB interface and the correct image information will be displayed automatically (by the display module) on the next frame (vertical sync.), when there is returned from out of the range to in range RGB interface timings.

All 3 kinds of bus width can be available during RGB interface mode (selected by COLMOD (17H) command for 6-bit, 16-bit and 18-bit data width)

| 17H | D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3         | D2 | D1 | D0 | Bus width   |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|------------|----|----|----|-------------|

| 50h | R4  | R3  | R2  | R1  | RO  | х   | G5  | G4  | G3 | G2 | G1 | G0 | B4 | B3 | B2         | B1 | BO | х  | 16-bit data |

| 60h | R5  | R4  | R3  | R2  | R1  | RO  | G5  | G4  | G3 | G2 | G1 | G0 | B5 | B4 | <b>B</b> 3 | B2 | B1 | BO | 18-bit data |

| 17H | D17 | D16 | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3         | D2 | D1 | D0 | Bus width   |

|     | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х  | Х  | R5 | R4 | R3 | R2 | R1         | RO | х  | х  |             |

| E0h | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х  | Х  | G5 | G4 | G3 | G2 | G1         | G0 | х  | х  | 6-bit data  |

|     | ×   | х   | ×   | х   | ×   | х   | Х   | X   | Х  | ×  | B5 | B4 | B3 | B2 | B1         | BO | х  | х  |             |

Note: (1) When 17H="E0h", 6-bit data width of 3-time transfer is used to transmit 1 pixel data with the 18-bit color depth information.

(2) Only 17H= "50h", "60h", "E0h" are valid on RGB I/F, others are invalid.

### **RGB** interface mode

| RGB I/F Mode | DOTCLK | DE       | VS   | HS   | Video Data bus<br>DB [B:0] | Register for Blanking<br>Porch setting |

|--------------|--------|----------|------|------|----------------------------|----------------------------------------|

| RGB Mode 1   | Used   | Used     | Used | Used | Used                       | Not Used                               |

| RGB Mode 2   | Used   | Not Used | Used | Used | Used                       | Used                                   |

There are 2 kinds of RGB mode which is selected by RCM1 & RCM0 hardware pins.

**In RGB Mode 1** (RCM1, RCM0 = "10"), writing data to display is done by DOTCLK and Video Data Bus (DB [17:0]), when DE is high state. The external synchronization signals (DOTCLK, VS and HS) are used for internal display signals. So, controller (host) must always transfer DOTCLK, VS, HS and DE signals to driver.

**In RGB Mode 2** (RCM1, RCM0 = "11"), blanking porch setting of VS and HS signals are defined by R33h and R34h command. DE pin is not used.

# 7-10 Color order on RGB interface

The meaning of the pixel information, when 3 components/pixel (Red, Green and Blue) on RGB interface are used, is describing on the following table:

| Pixel Color | R Component    | G Component    | B Component    |

|-------------|----------------|----------------|----------------|

| Black       | All bits are 0 | All bits are 0 | All bits are 0 |

| Blue        | All bits are 0 | All bits are 0 | All bits are 1 |

| Green       | All bits are 0 | All bits are 1 | All bits are 0 |

| Cyan        | All bits are 0 | All bits are 1 | All bits are 1 |

| Red         | All bits are 1 | All bits are 0 | All bits are 0 |

| Magenta     | All bits are 1 | All bits are 0 | All bits are 1 |

| Yellow      | All bits are 1 | All bits are 1 | All bits are 0 |

| White       | All bits are 1 | All bits are 1 | All bits are 1 |

Note: There are only defined main colors on this table - Not all gray levels of colors.

# 7-11 RGB data color coding

18-bits/pixel Colors Order on 6-bit Data width RGB Interface (RGB 6-6-6-bit input). There is 1 pixel (3 sub-pixels) per 3 bytes, 262K-colors, 17H="E0h"

Note: (1) The data order is as follows, MSB=D7, LSB=D0 and picture data is MSB=Bit7, LSB=Bit0 for Red, Green and Blue data. (3-trandfer data one pixel)

(2) '-' Don't care, but need to set IOVCC or VSSD level.

16-bits/pixel Colors Order on the 16-bits Data width RGB Interface (RGB 5-6-5-bits input). There is 1 pixel (3 sub-pixels) per byte, 65K-colors, 17H="50h"

- Note: (1) The data order is as follows, MSB=D17, LSB=D0 and picture data is MSB=Bit5, LSB=Bit0 for Green data and MSB=Bit4, LSB=Bit0 for Red and Blue data.

- (2) '-' Don't care, but need to set IOVCC or VSSD level.

18-bits/pixel Colors Order on the 18-bit Data width RGB Interface (RGB 6-6-bit input). There is 1 pixel (3 sub-pixels) per byte, 262K-colors, 17H="60h"

Note: (1) The data order is as follows, MSB=D17, LSB=D0 and picture data is MSB=Bit5, LSB=Bit0 for Red, Green and Blue data.

(2) '-' Don't care, but need to set IOVCC or VSSD level.

# 7-12 Instruction List

LCD Driver/Controller IC:HX8347-D

| (Hex)    | Operation                           | W/R        | Upper<br>Code     |               |                          |              | Low          | er Code      |              |                  |              | Comment |

|----------|-------------------------------------|------------|-------------------|---------------|--------------------------|--------------|--------------|--------------|--------------|------------------|--------------|---------|

| (IICA)   | Code                                |            | D[17:8]           | D7            | D6                       | D5           | D4           | D3           | D2           | D1               | D0           |         |

| 00       | Himax ID                            | R          | -                 | 0             | 1                        | 0            | 0            | 0            | 1            | 1                | 1            | -       |

| 01       | Display Mode<br>control             | W/R        | -                 | DP_S<br>TB(0) | DP_STB<br>_S(0)          | •            | -            | SCROL<br>(0) | IDMON<br>(0) | INVON<br>(0)     | PTLON<br>(0) | -       |

| 02       | Column address<br>start 2           | W/R        | -                 |               |                          | 1            | SC[15:8] (8  | 3'b0000_00   | 000)         |                  |              | -       |

| 03       | Column address<br>start 1           | W/R        | •                 | 9             |                          | )            | SC[7:0] (8   | 'b0000_00    | 00)          |                  |              | -       |

| 04       | Column address<br>end 2             | W/R        |                   |               | EC[15:8] (8'b0000_0000)  |              |              |              |              |                  |              |         |

| 05       | Column address<br>end 1             | W/R        | -                 |               | EC[7:0] (8'b1110_1111)   |              |              |              |              |                  |              |         |

| 06       | Row address<br>start 2              | W/R        | -                 |               |                          | 1            | SP[15:8] (8  | 3'b0000_00   | 000)         |                  |              | -       |

| 07       | Row address<br>start 1              | W/R        | -                 |               |                          | ;            | SP[7:0] (8'  | b0000_000    | 000)         |                  |              |         |

| 08       | Row address<br>end 2                | W/R        | -                 |               |                          |              | EP[15:8] (8  | 3'b0000_00   | 001)         |                  |              | -       |

| 09       | Row address<br>end 1                | W/R        | -                 |               |                          |              | EP[7:0] (8   | 'b0011_11    | 11)          |                  |              | -       |

| 0A       | Partial area start<br>row 2         | W/R        | -                 |               |                          | F            | PSL[15:8] (  | 8'b0000_0    | 000)         |                  |              | -       |

| 0B       | Partial area start<br>row 1         | W/R        | -                 |               |                          | F            | PSL[7:0] (8  | 'b0000_00    | 000)         |                  |              | -       |

| 0C       | Partial area end<br>row 2           | W/R        | -                 |               |                          | F            | PEL[15:8] (  | 8'b0000_0    | 001)         |                  |              | -       |

| 0D       | Partial area end                    | W/R        | -                 |               |                          |              | PEL[7:0] (   | B'b0011_1    | 111)         |                  |              |         |

| 0E       | row 1<br>Vertical Scroll            | W/R        | -                 |               | TFA[15:8] (8'b0000_0000) |              |              |              |              |                  |              |         |

| 0F       | Top fixed area 2<br>Vertical Scroll | W/R        |                   |               |                          |              | TFA[7:0] (8  |              |              |                  |              | 2       |

| 10       | Top fixed area 1<br>Vertical Scroll | W/R        | -                 |               | VSA[15:8] (8'b0000_0001) |              |              |              |              |                  | -            |         |

| 11       | height area 2<br>Vertical Scroll    | W/R        | -                 | -             | VSA[7:0] (8'b0100_0000)  |              |              |              |              |                  |              | -       |

| 12       | height area 1<br>Vertical Scroll    | W/R        | -                 |               |                          |              | BFA[15:8] (  | 2.00         |              |                  |              | -       |

| 13       | Button area 2<br>Vertical Scroll    | W/R        |                   |               |                          |              | 3FA [7:0] (8 |              |              |                  |              | -       |

| 14       | Button area 1<br>Vertical Scroll    | W/R        | - 67              |               |                          |              | SP [15:8]    | n Bala       |              |                  |              |         |

| 15       | Start address 2<br>Vertical Scroll  | W/R        | $\mathcal{P}_{0}$ |               |                          |              | /SP [7:0] (i |              |              |                  |              |         |

| 16       | Start address 1<br>Memory Access    | W/R        | ×.                | MY(0)         | MX(0)                    | MV(0)        | ML(0)        | BGR(0)       | -            |                  |              |         |

|          | control                             | $\sim$     |                   | Mir (0)       |                          |              |              | Bont(0)      | 15           |                  | 110          |         |

| 17<br>18 | COLMOD<br>OSC Control 2             | W/R<br>W/R | -                 | 1/            |                          | 0] (4b'0110) |              |              |              | PF[2:0] (3b'     |              | -       |

| 10       | OSC Control 1                       | W/R        | -                 | -             | PI_RADJI                 | [3:0] (3b'00 | -            | -            | -            | 0[3:0](4b'010    | OSC_E        | · ·     |

| 1A       | Power Control 1                     | W/R        |                   |               |                          | -            | 1.12         |              |              | BT[2:0] (00*     | N(0)         | -       |

| 1B       | Power Control 2                     | W/R        |                   |               |                          | -            | · · · · ·    | VRH[5:0] (   | 01_1011)_4   |                  | .)           |         |

| 10       | Power Control 3                     | W/R        | -                 |               |                          | 1            |              | -            |              | AP[2:0] (01      | 1)           | 2       |

| 1D       | Power Control 4                     | W/R        | -                 |               |                          | I_FS0[2:0](  | 100)         | -            | 2            | P_FS0[2:0] ]     |              | -       |

| 1E       | Power Control 5                     | W/R        | -                 | -             |                          | FS1[2:0]     |              |              |              | P_FS1[2:0] ]     |              | -       |

| 1F       | Power Control 6                     | W/R        |                   | GASEN(1)      | VCOMG(0                  | 1            | PON(0)       | DK(1)        | XDK(0)       | DDVDH_<br>TRI(0) | STB(1)       | -       |

| 22       | SRAM Write<br>Control               | W/R        |                   |               |                          |              | SRAM W       | /rite        |              |                  |              | -       |

| 23       | VCOM Control 1                      | W/R        | -                 | 1             |                          |              | VMF[7:0]     | (1000_000    | 00)          |                  |              | -       |

| 24       | VCOM Control 2                      | W/R        | -                 |               |                          |              |              | (0111_000    |              |                  |              | -       |

| 25       | VCOM Control 3                      | W/R        | -                 | 1             |                          | 21.5         |              | (0010_111    |              |                  |              | -       |

| 26       | Display Control 1                   | W/R        |                   |               | -                        | -            | -            |              |              | 6:0](0001)       |              | -       |

| 27       | Display Control 2                   | W/R        | -                 | PT[1          | :0](10)                  | PTV          | 1:0](10)     | -            | -            | PTG(1)           | REF(1)       | -       |

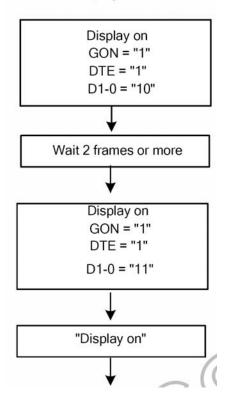

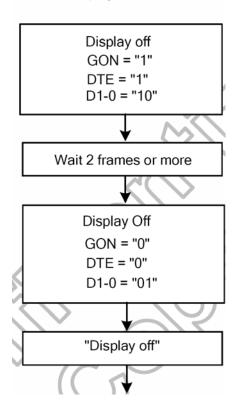

| 28       | Display Control 3                   | W/R        | -                 | -             | -                        | GON(1)       |              | DI1          | :0] (00)     | -                | -            | -       |

| (Hex)    | Operation                          | W/R          | Upper<br>Code |          |                        |                        | Low                 | ver Code            |                            |               |                | Comment |

|----------|------------------------------------|--------------|---------------|----------|------------------------|------------------------|---------------------|---------------------|----------------------------|---------------|----------------|---------|

| (,       | Code                               |              | D[17:8]       | D7       | D6                     | D5                     | D4                  | D3                  | D2                         | D1            | D0             |         |

| 29       | Frame Rate<br>control 1            | W/R          | -             |          | I/PI_RTN               | [3:0](0010)            |                     |                     | N/P_RT                     | N[3:0](0010)  |                | 4       |

| 2A       | Frame Rate<br>Control 2            | W/R          | -             |          | -                      | I/PI_DIV               | [1:0](00)           | 8                   | -                          | N/P_DIV       | [1:0](00)      |         |

| 2B       | Frame Rate<br>Control 3            | W/R          | -             |          |                        | N/I                    | P_DUM[7:0           | 0] (8b'0001         | 1_1100)                    |               |                | -       |

| 2C       | Frame Rate<br>Control 4            | W/R          |               |          |                        |                        | PI_DUM[7:0          |                     |                            |               |                |         |

| 2D       | Cycle Control 1                    | W/R          |               | 1        |                        |                        | DON[7:0]            |                     |                            |               |                | -       |

| 2E<br>2F | Cycle Control 2                    | W/R<br>W/R   | -             |          | 1/01                   |                        | SDOF[7:0]           | (8'00111_           |                            | NIM/[2:01/2b  | 2001)          | -       |

|          | Display inversion<br>RGB interface | 10.0220.0220 | -             | -        | 1/PI_                  | NW[2:0](3b             | 1                   | · ·                 | IN/P                       | NW[2:0] (3b   |                | -       |

| 31       | control 1<br>RGB interface         | W/R          | -             | -        | -                      | -                      | -                   | -<br>DPL            | -<br>HSPL                  | RCM[1         | :0](00)<br>EPL | -       |

| 32       | control 2<br>RGB interface         | W/R          | -             | -        | -                      |                        | -                   | (0)                 | (0)                        | (0)           | (0)            |         |

| 33       | control 3                          | W/R          | -             |          |                        |                        | HE                  | 3P[7:0]             |                            |               |                |         |

| 34       | RGB interface<br>control 4         | W/R          | •             | HBF      | P[9:8]                 |                        |                     |                     | BP[5:0]                    |               |                | ÷       |

| 36       | Panel<br>Characteristic            | W/R          |               |          | ~                      | -                      | -                   | SS_P<br>anel        | GS_Pan<br>el               | REV_Pa<br>nel | BGR_P<br>anel  |         |

| 38       | OTP Control 1                      | W/R          |               | OTP_F    | PTM[1:0]               | OTP_VA                 | RDJ[1:0]            | OTP_<br>POR         | OTP_O<br>TPEN              | OTP_PP<br>ROG | OTP_P<br>WE    | ÷       |

| 39       | OTP Control 2                      | W/R          | -             | -        | -                      | -                      | -                   | -                   | OTP_Y<br>A2                | OTP_YA1       | OTP_Y<br>A0    | -       |

| ЗA       | OTP Control 3                      | W/R          | -             | -        | -                      | -                      | OTP_X<br>A4         | OTP_<br>XA3         | OTP_X<br>A2                | OTP_XA1       | OTP_XA0        |         |

| 3C       | CABC Control 1                     | W/R          | -             |          |                        |                        | DBV[                | 7:0](8'h00)         |                            |               |                | -       |

| 3D       | CABC Control 2                     | W/R          | -             |          | -                      | BCTRL<br>(0)           | (1)                 | DD<br>(0)           | BL<br>(0)                  | 5 -           |                |         |

| 3E       | CABC Control 3                     | W/R          | -             | ÷        | -                      | 12                     | $\geq$              | R                   | 9                          | C1<br>(0)     | C0<br>(0)      | •       |

| 3F       | CABC Control 4                     | W/R          | -             |          |                        |                        | CMB[                | 7:0](8'h00)         |                            |               |                | -       |

| 40       | r1 Control (1)                     | W/R          | -             | -        | VRP0[5:0] (6'b00_0001) |                        |                     |                     |                            |               | -              |         |

| 41       | r1 Control (2)                     | W/R          |               | -        | CO                     | VRP1[5:0] (6'b00_1110) |                     |                     |                            |               |                |         |

| 42       | r1 Control (3)                     | W/R          | -             | -        | $\left( \cdot \right)$ |                        |                     |                     | ] (6'b01_00                |               |                |         |

| 43       | r1 Control (4)<br>r1 Control (5)   | W/R<br>W/R   | -             | -        | 2                      |                        |                     |                     | ] (6'b01_10<br>] (6'b01_10 |               |                | -       |

| 45       | r1 Control (6)                     | W/R          | -             | 1        |                        |                        |                     |                     | ] (6'b10 01                |               |                |         |

| 46       | r1 Control (7)                     | W/R          | -             | 25       | _                      |                        | PRP                 | 0[6:0] (7'b0        |                            | 00)           |                |         |

| 47       | r1 Control (8)                     | W/R          | -             |          |                        |                        |                     | 1[6:0] (7'b1        |                            |               |                | -       |

| 48       | r1 Control (9)                     | W/R          | - 697         | NY I     | -                      | 11                     |                     |                     | P0[4:0] (5'b               | 0 1011)       |                | 2       |

| 49       | r1 Control (10)                    | W/R          | ~.(           | η.       | -                      | ~~                     |                     |                     | P1[4:0] (5'b               |               |                | -       |

| 4A       | r1 Control (11)                    | W/R          | 1.            | -        | $\langle \cap \rangle$ |                        | °                   |                     | P2[4:0] (5'b               |               | Î              |         |

| 4B       | r1 Control (12)                    | W/R          | 1.            | $\sim$   | $(\odot)$              | -                      |                     | PKF                 | P3[4:0] (5'b               | 1_1010)       |                |         |

| 4C       | r1 Control (13)                    | W/R          | V.            | 10       |                        | -                      | 4                   |                     | P4[4:0] (5'b               |               |                | 1       |

| 50       | r1 Control (14)                    | W/R          | <sup>-</sup>  | (-)      | ) -                    |                        |                     |                     | ] (6'b01_10                |               |                |         |

| 51       | r1 Control (15)                    | W/R          | -             | <u> </u> | -                      |                        |                     |                     | ] (6'b10_01                |               |                |         |

| 52       | r1 Control (16)                    | W/R          | -             | ~        | -                      |                        |                     |                     | (6'b10_01                  |               |                | -       |

| 53       | r1 Control (17)                    | W/R          | -             |          | -                      |                        |                     |                     | ] (6'b10_11                |               |                | -       |

| 54<br>55 | r1 Control (18)<br>r1 Control (19) | W/R<br>W/R   | -             | -        | -                      |                        |                     |                     | ] (6'b11_00<br>] (6'b11_11 |               |                | -       |

| 56       | r1 Control (19)                    | W/R          | -             | -        | -                      |                        | PRNO                |                     | 01_1010)                   | (0)           |                | -       |